# CubeSat Kit™ Motherboard Module 2 (MBM2)

Hardware Revision: F

## Motherboard with BeagleBone Black (BBB) SBC

### **Applications**

- CubeSat nanosatellites

- SUPERNOVA™ nanosatellites

- Balloon missions

#### **Features**

- For use with 104-pin CubeSat Kit™ Bus

- Hosts BeagleBone® Black (BBB) SBC as a single 0.600" tall CSK-compatible module

- Custom Linux-based image on BBB:

- Pumpkin FSW SupMCU service

- Drivers for BBB and MBM2 peripherals

- Python & Perl pre-installed

- Ready for user scripts & applications

- Multiple +5V power sources supported, auto-selected

- BBB Ethernet, USB host & USB device ports fully supported

- BBB signal availability:

- 4.5x UART, 1xSPI, 1x I2C & 6x GPIO on CSK Bus Connector

- 7x analog input (0-1.8Vdc) on CSK Bus Connector

- RS422+LVTTL UART/SPI/GPIO on 25-pin high-density PHY connector

- 5x GPIO on 6-pin DF13 connector

- UART0 breakout on 4-pin FPC connector

- Power-on fully protected I/O

- On-board reset circuitry, drives BBB's sys Resetn and GPIO buffers

- On-board SD Card interface (SPI mode)

- On-board Real-Time Clock (RTC) with battery backup

- On-board -RESET & OFF\_vcc-driven WDT interface

- Independent latchup (device overcurrent) protection on critical subsystems

#### ORDERING INFORMATION

Pumpkin P/N 710-01362

| Option<br>Code    | CubeSat Kit Bus Connector |

|-------------------|---------------------------|

| /00<br>(standard) | stackthrough              |

| /01               | non-stackthrough          |

Contact factory for availability of optional configurations.

Option code /00 shown.

#### **CAUTION**

Electrostatic Sensitive Devices

Handle with Care

- PC/104-size footprint

- Stackable 104-pin CubeSat Kit Bus connectors includes processor's complete I/O space, user-assignable signals and more

- Wiring-free module interconnect scheme

- 6-layer gold-plated blue-soldermask PCB with ground plane for enhanced signal integrity

# **CHANGELOG**

| Rev. | Date            | e Author Comments |                                                                                                                          |  |

|------|-----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| Α    | 20200712        | AEK               | Initial release of hardware Rev F.                                                                                       |  |

| A1   | A1 20221207 AEK |                   | Corrected signal type of VDD_ADC and descriptions of AN[60]. Updated block diagram to reflect ADC subsystem corrections. |  |

| A2   | A2 20240701 AEK |                   | Updated to reflect the pre-installed software on the BBB at delivery.                                                    |  |

|      |                 |                   |                                                                                                                          |  |

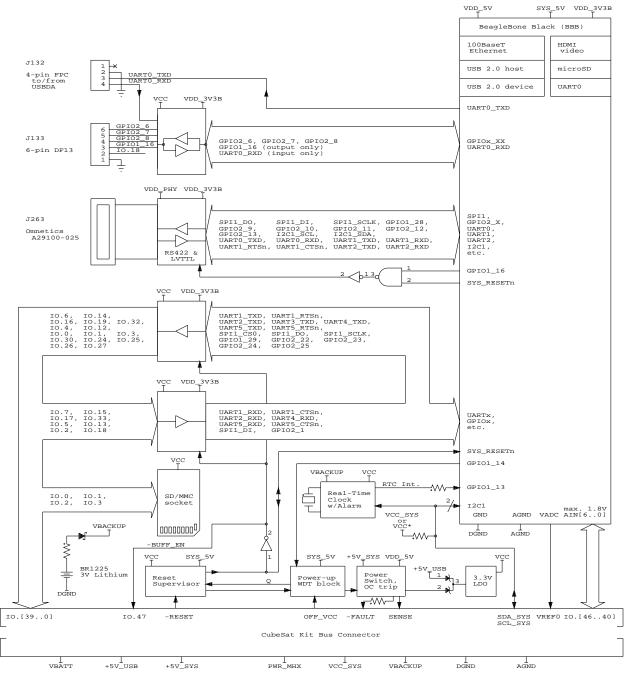

### **OPERATIONAL DESCRIPTION**

The Motherboard Module 2 (MBM2) is a CubeSat Kit (CSK)-compatible host for the COTS BeagleBone Black (BBB) Rev C single-board computer and compatible variants thereof. When installed onto an MBM2, the BBB interfaces to the CSK electrical bus via standardized signals. Additional features like a Real-Time Clock (RTC) with battery backup and a full-size SD Card operating in SPI mode are also provided. This MBM2+BBB combination can serve as the on-board computer (OBC) for a wide range of small satellites and similar equipment.

#### **INCLUDED SOFTWARE**

The BBB on the MBM2 comes pre-installed with a running image of Pumpkin's flight software (FSW) SupMCU service; no source code is provided. The FSW SupMCU service is written entirely in Rust. This service provides the MBM2 user with the following functionality for communicating with Pumpkin SupMCU modules:

- Discover all available SupMCU modules<sup>2</sup> connected to the MBM2, and inspect available:

- SCPI commands

- Telemetry fields & formats

- I2C address

- Send SCPI commands to SupMCU modules over I2C<sup>3</sup>

- Request telemetry from SupMCU modules over I2C

- Apply firmware updates to SupMCU modules over I2C

The MBM2 user can access the pre-installed GraphQL playground (via visiting http://<ip-address-of-bbb>:8150 when connected to the MBM2 over Ethernet) to send telemetry requests without any scripting knowledge. Users can also write scripts or compiled applications to make a GraphQL request over HTTP to the SupMCU FSW endpoint on port 8150 for telemetry, SCPI commanding, firmware updates and module discovery.

The BBB supports running custom and user-created applications on it. Users write custom applications to interface to connected payloads, to interface to other bus modules<sup>4</sup> and to interact with SupMCU modules on behalf of the application(s). The written applications will typically interface over UART, SPI or Ethernet for connected payloads, and receive commands over Ethernet (or other available interfaces) to interact with the connected payload on behalf of the user. Custom applications can be written to carry out a number of other tasks as well, such as:

- Command and data handling (C&DH)

- Radio communications

- Third-party COTS hardware interfaces

- Mission operational modes & logic

Python 3.10.9 & Perl 5.34 are pre-installed on the BBB for basic scripting functionality. No additional libraries are installed beyond the Python/Perl standard libraries. By default, no Perl CPAN modules have been pre-installed. MBM2 users can compile any C/C++/Rust applications via targeting the `armv7-unknown-linux-gnueabihf` with GLIB <=2.35 as the target. Alternatively, users can target `armv7-unknown-linux-musleabihf` to avoid depending on GLIB. The custom Linux image installed onto the BBB uses `systemd` to start services on the device (e.g., the FSW SupMCU service) and the user can write their own service files to be run on demand, via trigger or on boot.

The BBB image has drivers for the following MBM2+BBB peripherals pre-installed:

\_

<sup>&</sup>lt;sup>1</sup> This service is one of several components of Pumpkin's GUTS FSW. The GUTS FSW is not included with the MBM2 and can be purchased separately.

<sup>&</sup>lt;sup>2</sup> All of Pumpkin's flight modules include a supervisory MCU (aka SupMCU). Examples of SupMCU modules are the EPSM1 electrical power system, the BM2 intelligent battery module, the GPSRM1 GNSS receiver, etc.

<sup>&</sup>lt;sup>3</sup> See the online SupMCU Firmware Reference Manual at <a href="https://pumpkin-space-systems.gitlab.io/public/software-reference-manual/index.html">https://pumpkin-space-systems.gitlab.io/public/software-reference-manual/index.html</a> for more information on all things about Pumpkin SupMCUs and communicating with them.

<sup>&</sup>lt;sup>4</sup> E.g., radios, ADC systems, thrusters, etc.

- RTC clock (M41T81S)

- Ethernet PHY

- I2C1 (used for SupMCU communications)

- SPI1 (for use with MBM2's full-size SD Card socket or with CubeSat Kit bus peripherals)

- UART0-5 (UART5 is TX only)<sup>5</sup>

- USB 2.0 host

The user can remote terminal via secure shell (SSH) into the BBB over Ethernet with the following credential sets by default (in format of user/password):

- FSW SupMCU service user: guts/pumpkinguts. Non-root user for non-administrative commands. The `guts` user can also use the `sudo` command to elevate permissions.

- Root user: root/pumpkinroot. Root user for running series of administrative commands. Use the `guts` user for typical usage.

Please be sure to change these passwords via 'passwd' when logged in as 'guts' or 'root'.

Please refer to the minimal Pumpkin GUTS User Manual for usage examples.

Pumpkin makes the original Pumpkin-source Linux image available, should the user prefer to install a different Linux image and then revert back to a Pumpkin Linux image for the BBB at a later time.

-

<sup>&</sup>lt;sup>5</sup> UART0 is the dedicated Linux serial debug interface for the BBB. It is not available as a general-purpose UART.

#### HARDWARE DESCRIPTION

Power-on and reset behavior of the combined MBM2+BBB is carefully controlled to ensure proper operation and protection of BBB I/O when interfacing to other modules through the CSK bus connector. This is accomplished via high-speed, zero-power level-shifter / isolators between the BB and the CSK bus connector. The isolators are disabled while the BBB is in reset, and are enabled once the BBB comes out of reset and is ready to handle signals at its I/O pins. This protection prevents non-phased power sequencing within the CSK architecture from damaging the BBB's I/O.<sup>6</sup>

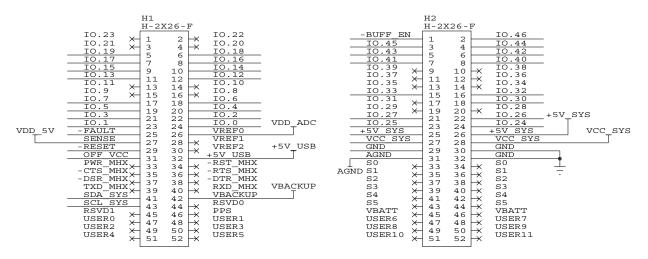

Four and a half UARTs (two with -CTS/-RTS flow control), one SPI, one I2C, five general-purpose outputs and one general-purpose input are mapped between the BBB and the CSK bus connector. Additionally, seven dedicated analog inputs are mapped from the CSK bus connector to the BBB's analog inputs.

| BBB Signal | Description                 | CSK Signal                                                                                                                                        |  |  |  |  |

|------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| UART1_RXD  | BBB UART 1 receive          |                                                                                                                                                   |  |  |  |  |

| UART1_TXD  | BBB UART 1 transmit         | The "second" CSK UART (Ux1), with flow control. Historically, this serial                                                                         |  |  |  |  |

| UART1_RTSn | BBB UART 1 flow control     | channel has been used to communicate with a radio / modem.                                                                                        |  |  |  |  |

| UART1_CTSn | BBB UART 1 flow control     |                                                                                                                                                   |  |  |  |  |

| UART2_RXD  | BBB UART 2 receive          | The "third" CSK UART (Ux2), without flow control. Historically, this serial channel has been used to communicate with a GPS receiver and/or other |  |  |  |  |

| UART2_TXD  | BBB UART 2 transmit         | serial devices.                                                                                                                                   |  |  |  |  |

| UART3_TXD  | BBB UART 3 transmit         | The "fifth" CSK UART (Ux4), transmit only.                                                                                                        |  |  |  |  |

| UART4_RXD  | BBB UART 4 receive          | The "fourth" CSK UART (Ux3), without flow control. Historically, this serial                                                                      |  |  |  |  |

| UART4_TXD  | BBB UART 4 transmit         | channel has been used to communicate with a GPS receiver and/or other serial devices.                                                             |  |  |  |  |

| UART5_RXD  | BBB UART 5 receive          |                                                                                                                                                   |  |  |  |  |

| UART5_TXD  | BBB UART 5 transmit         | The "first" CSK UART (Ux0), with flow control. Historically, this serial channel                                                                  |  |  |  |  |

| UART5_RTSn | BBB UART 5 flow control     | has been used to communicate with an ADACS.                                                                                                       |  |  |  |  |

| UART5_CTSn | BBB UART 5 flow control     |                                                                                                                                                   |  |  |  |  |

| SPI1_SCLK  |                             |                                                                                                                                                   |  |  |  |  |

| SPI1_DO    | BBB SPI 1 interface         | The "first" CSK SPI (SPI0). Historically, this interface has been used to                                                                         |  |  |  |  |

| SPI1_DI    | BBB 3F1 Tillellace          | communicate with an SD card hosting a FAT filesystem.                                                                                             |  |  |  |  |

| SPI1_CS0   |                             |                                                                                                                                                   |  |  |  |  |

| GPIO2_22   |                             |                                                                                                                                                   |  |  |  |  |

| GPI02_23   | BBB general-purpose output  | General-purpose output                                                                                                                            |  |  |  |  |

| GPIO2_24   | BBB general-purpose output  | General-purpose dutput                                                                                                                            |  |  |  |  |

| GPI02_25   |                             |                                                                                                                                                   |  |  |  |  |

| GPI02_1    | BBB general-purpose input   | General-purpose input                                                                                                                             |  |  |  |  |

| I2C1_SDA   | BBB I2C data                | The "first" I2C. Historically, this interface has been used to communicate with                                                                   |  |  |  |  |

| I2C1_SCL   | BBB I2C clock               | various subsystems.                                                                                                                               |  |  |  |  |

| AN6 - ANO  | BBB AIN6-AIN0 analog inputs | Analog inputs to the host (BBB)                                                                                                                   |  |  |  |  |

| AN7        |                             | -BUFF_EN output, indicates when active that the BBB's I/O is actively connected to the CSK Bus Connector                                          |  |  |  |  |

Table 1: MBM2 BBB-to-CSK bus connector digital signal mappings

BBB features that remain untouched and that can be used independently of the CSK bus connector include:

- Ethernet (via 100BASET / RJ45)

- USB host (via USB type A)

- USB device (via USB micro-B)

- HDMI (via micro-HDMI)

- SD card (via micro-SD socket)

- COM0/UART0 (via 1x6 SIP header)

- External +5Vdc power (via 2.1/5.5mm barrel jack)

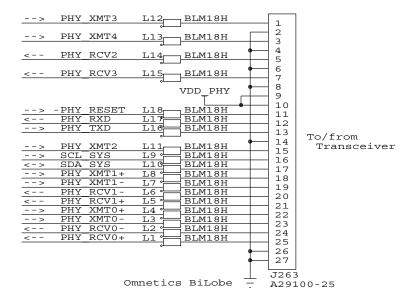

Additionally, several signals are mapped from the BBB and MBM2 to a dedicated Omnetics® BiLobe 25-pin connector J263 that is used as a physical interface (PHY) to a high-speed module/payload external to the MBM2. Some of the BBB signals on the PHY are unique to the PHY; others are common to the signals that are mapped to the CSK bus connector and can be used on the CSK bus connector OR on J263, but not both.

| Signal Name(s) | BBB Signal | Interface / Level | Notes |

|----------------|------------|-------------------|-------|

<sup>&</sup>lt;sup>6</sup> The I/O protection afforded by the MBM2's I/O isolators applies only to digital I/O. The BBB's analog inputs are connected directly to the BBB's analog input pins. Users should control analog inputs to the BBB via the -BUFF EN output signal.

\_

| PHY_XMT0+ PHY_XMT0-  PHY_XMT1+ PHY_XMT1-  PHY_RCV0+ PHY_RCV0-  PHY_RCV1+ PHY_RCV1- | UART1_TXD Of SPI1_DO UART1_RTSN OF UART2_TXD OF SPI1_SCLK UART1_RXD OF SPI1_DI UART1_CTSN OF UART2_RXD OF UART2_RXD OF | RS422 with configurable series and/or and parallel termination. Uses TI SN65HVD73 (20Mbps) RS485 transceivers. | Supports multiple configurations, including:  • RS422 UART1_TXD/RXD and UART1_RTSn/CTSn  • RS422 UART1_TXD/RXD and UART2_TXD/RXD  • RS422 SPI1-over-RS422 with DO, DI, SCLK and -CS signals  Use of any of these signal sets (UART1, UART2 and SPI1) precludes their use on the CSK bus connector. |  |  |  |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                    | GPIO1_28                                                                                                               |                                                                                                                |                                                                                                                                                                                                                                                                                                    |  |  |  |

| PHY_XMT2                                                                           | GPIO2_9                                                                                                                |                                                                                                                |                                                                                                                                                                                                                                                                                                    |  |  |  |

| PHY_XMT3                                                                           | GPIO2_10                                                                                                               |                                                                                                                | These single-ended BBB outputs and inputs are always                                                                                                                                                                                                                                               |  |  |  |

| PHY_XMT4                                                                           | GPIO2_11                                                                                                               |                                                                                                                | available, since these BBB signals are not mapped to the CSK bus connector.                                                                                                                                                                                                                        |  |  |  |

| PHY_RCV2                                                                           | GPI02_12                                                                                                               |                                                                                                                |                                                                                                                                                                                                                                                                                                    |  |  |  |

| PHY_RCV3                                                                           | GPI02_13                                                                                                               |                                                                                                                |                                                                                                                                                                                                                                                                                                    |  |  |  |

| PHY_TXD                                                                            | UARTO_TXD<br>Or<br>UART2_TXD                                                                                           | LVTTL at VDD_PHY rail<br>(+3.3V or +5V) levels                                                                 | Supports multiple configurations, including:  Single-ended UARTO_TXD/RXD Single-ended UART2_TXD/RXD                                                                                                                                                                                                |  |  |  |

| PHY_RXD                                                                            | UARTO_RXD<br>Or<br>UART2_RXD                                                                                           |                                                                                                                | Use of UART0 precludes its use on J132. Use of UART2 precludes its use on the CSK bus connector.                                                                                                                                                                                                   |  |  |  |

| SDA_SYS                                                                            | I2C1_SDA                                                                                                               | Pulled up to 3.3V on MBM2.                                                                                     | These signals are essentially an extension of the CSK bus                                                                                                                                                                                                                                          |  |  |  |

| SCL_SYS                                                                            | I2C1_SDA                                                                                                               | Fulled up to 3.3V on MBM2.                                                                                     | I2C signals.                                                                                                                                                                                                                                                                                       |  |  |  |

Table 2: MBM2 PHY connector J263 signal mappings

A 6-pin Hirose DF13 right-angle header **J133** is provided with five BBB GPIO signals, as described below. Each of the five signals is actively isolated and is only passed to/from the BBB once the BBB emerges from reset. Three of these signals are bidirectional; i.e., they can be used as inputs to or outputs from the BBB, with appropriate user software configuration of the corresponding BBB GPIO pins. The signals are at 3.3V LVTTL levels, and are +5V-tolerant.<sup>7</sup>

| Pin<br>Number | BBB/CSK<br>Signal | Signal Type       | Notes                                                                              |

|---------------|-------------------|-------------------|------------------------------------------------------------------------------------|

| 1             | DGND              |                   | Any remote signals connected to J133 should carry a ground reference back to J133. |

| 2             | 10.18             | 3.3V LVTTL input  | Connected directly to CSK's IO.18, which is an input to the BBB's GPIO2_1.         |

| 3             | GPI01_16          | 3.3V LVTTL output | Output from BBB's GPIO1_16.                                                        |

| 4             | GPIO2_8           | 3.3V LVTTL        | Input/output to/from BBB's gPIO2_8.                                                |

| 5             | GPIO2_7           | input/output      | Input/output to/from BBB's gPIO2_7                                                 |

| 6             | GPIO2_6           | inputoutput       | Input/output to/from BBB's GPIO2 6                                                 |

Table 3: MBM2 J133 signal mappings

A 4-pin FPC connector  $\mathfrak{J}132$  is provided to enable a connection to the BBB's UART0 serial port, which is used for BBB boot control and as a BBB debug terminal. A Pumpkin USB Debug Adapter (USBDA) is required to take advantage of this port.

Note that the BBB's UART0 is not available as a general-purpose UART. This limitation is due to BBB software architectural limits, as has nothing to do with the MBM2 per se.

\_

<sup>&</sup>lt;sup>7</sup> High-speed (e.g., 100kHz and higher) signals are not recommended for J133.

| Pin<br>Number | BBB/CSK<br>Signal | Signal Type       | Notes                                                   |

|---------------|-------------------|-------------------|---------------------------------------------------------|

| 1             |                   |                   | Not connected.                                          |

| 2             | DGND              |                   | Ground reference for serial UART.                       |

| 3             | UARTO_TXD         | 3.3V LVTTL output | Serial output from BBB's UARTO 1x6 serial header pin 5. |

| 4             | UARTO_RXD         | 3.3V LVTTL input  | Serial input to BBB's UARTO 1x6 serial header pin 4.    |

Table 4: MBM2 J132 signal mappings

An external watchdog timer (WDT) interface is provided.

The BBB operates from system +5Vdc power (+5v\_sys). BBB I/O (and therefore its I/O signals on the BBB bus connector) operates at +3.3V logic levels.

Note that unlike other Pumpkin Pluggable Processor Modules (PPMs) with general-purpose I/O mapped to the CSK bus connector, the MBM2 provides unidirectional signals (and power-on sequencing and protection) between the BBB and the CSK bus connector, on a per-GPIO-pin basis. Also, note that not all of the BBB's P8 and P9 pins are mapped to the CSK bus connector. Future revisions of the MBM2 may map additional BBB pins to the CSK bus connector, and/or may allow for bidirectional digital I/O signals.

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                | Symbol         | Value        | Units |

|--------------------------|----------------|--------------|-------|

| Operating temperature    | T <sub>A</sub> | -40 to +85   | °C    |

| Voltage on +5v_usb bus   |                | -0.3 to +6   | W     |

| Voltage on +5v_sys bus   |                | -0.3 10 +0   | V     |

| Voltage on vcc_sys bus   |                | -0.3 to +3.6 | \/    |

| Voltage on local vcc bus |                | -0.3 10 +3.0 | V     |

# PHYSICAL CHARACTERISTICS

| Parameter                                   | Conditions / Notes                                  | Symbol | Min | Тур     | Max | Units |

|---------------------------------------------|-----------------------------------------------------|--------|-----|---------|-----|-------|

| Mass                                        |                                                     |        |     | 34      |     | g     |

| Height of components above PCB              |                                                     |        |     |         | 11  | mm    |

| Height of components below PCB              | Not including stacking H1/H2 connectors             |        |     |         | 3.5 | mm    |

| PCB width                                   | Corner hole pattern matches                         |        |     | 96      |     | mm    |

| PCB length                                  | PC/104                                              |        |     | 90      |     | mm    |

| PCB thickness                               | FC/104                                              |        |     | 1.6     |     | mm    |

| CubeSat Kit Bus<br>Connector terminal pitch | Horizontal or vertical distance to nearest terminal |        |     | 2.54    |     | mm    |

| Pumpkin PCB P/N                             |                                                     |        | 70  | )5-0116 | 88  | ·     |

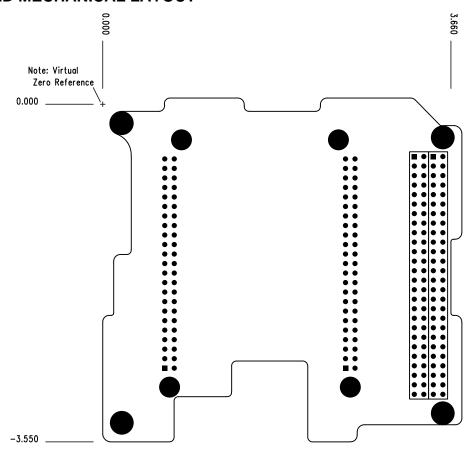

# SIMPLIFIED MECHANICAL LAYOUT 8

© Pumpkin, Inc. 2003-2024

$<sup>^{\</sup>rm 8}$  Dimensions in inches.

### **ELECTRICAL CHARACTERISTICS**

(T = 25°C, +5V bus = +5V unless otherwise noted)

| Parameter                                              | Conditions / Notes                               | Symbol                     | Min | Тур              | Max | Units |

|--------------------------------------------------------|--------------------------------------------------|----------------------------|-----|------------------|-----|-------|

| Maximum external dc voltage on +5v_sys or to P1 on BBB | Overvoltage will damage<br>MBM2 and/or BBB       | V <sub>+5V_IN_MAX</sub>    |     |                  | 6.0 | ٧     |

| Backup battery voltage                                 | Feeds <b>VBACKUP</b> through <b>R20</b> (4.7kΩ). | V <sub>BT1</sub>           |     | 3.0              | 3.5 | V     |

| Operating current                                      | Without BBB                                      | I <sub>OP_NO_BBB</sub>     |     | 10               |     | mA    |

| (exclusively from +5v_sys)                             | With BBB, Ethernet disabled                      | I <sub>OP_BBB_NO_ETH</sub> |     | 300              |     | mA    |

|                                                        | With BBB, Ethernet enabled                       | I <sub>OP_BBB_ETH</sub>    |     | 350              |     | mA    |

| RTC crystal frequency                                  | No external capacitors                           | $f_{	extsf{CLK}}$ RTC      | 32  | .768 ± 0.0       | 01  | kHz   |

| Overcurrent trip point for VDD_5v                      | Set by R1                                        | I <sub>TRIP_5V</sub>       |     | 920              |     | mA    |

| Overcurrent trip point for VDD_PHY                     | Set by R33                                       | I <sub>TRIP_PHY</sub>      |     | 920 <sup>9</sup> |     | mA    |

| Overcurrent trip point for +5v_usB                     | Set by R14                                       | I <sub>TRIP_USB</sub>      |     | 750              |     | mA    |

| Data rate through any on-board isolator (U1-U3)        |                                                  |                            | 50  |                  |     | MHz   |

| Parameter                                | Conditions / Notes                           | Min | Тур      | Max | Units |

|------------------------------------------|----------------------------------------------|-----|----------|-----|-------|

| I2C addresses available to slave devices | Set by BBB (I2C Master, 7-bit addresses)     |     | 0x04-0x7 | 'F  |       |

| I2C clock speed                          |                                              |     | 400      |     | kHz   |

| I2C pull-up resistors                    | Pull-up resistors R83 & R84 <sup>10,11</sup> |     | 1.5k     |     | Ω     |

\_

<sup>&</sup>lt;sup>9</sup> Default value. +3.3V Source supply VDD 3V3B may not be capable of delivering this much current.

<sup>&</sup>lt;sup>10</sup> Default value. Users should evaluate the I2C bus performance in their particular application and replace these resistors with optimal values.

optimal values.

11 The MBM2 supports pull-ups to two different voltage sources (local vcc and vcc\_sys). Consult the MBM2 schematics for more information.

### **BLOCK DIAGRAM**

Zero-Ohm jumpers and pull-down resistors associated with different configurations are not shown.

<sup>\*:</sup> Default configuration, selectable via resistors or 0-Ohm resistors.

### **CubeSat Kit Bus PIN DESCRIPTIONS**

### CubeSat System Bus

### CubeSat Kit Bus PIN DESCRIPTIONS - I/O

| Name  | Pin     | I/O | Description                                                                  |

|-------|---------|-----|------------------------------------------------------------------------------|

| 10.0  | H1.24   | 0   | -cs sp. Controls SD Card interface. Part of the MBM2's SD card interface.    |

| 10.0  | П1.24   | O   | Output from the BBB's SPI1_CS0.                                              |

| 10.1  | H1.23   | 0   | SDO0. SPI master data out. Part of the MBM2's SD card interface. Output      |

| 10.1  | П1.23   | O   | from the BBB's SPI1_DO.                                                      |

| 10.2  | H1.22   |     | SDIO. SPI master data in. Part of the MBM2's SD card interface. Input to the |

| 10.2  | П1.22   | ı   | BBB's SPI1_DI.                                                               |

| 10.3  | H1.21   | 0   | SCKO. SPI clock. Part of the MBM2's SD card interface. Output from the       |

| 10.3  | П1.21   | O   | BBB's SPI1_SCLK.                                                             |

| 10.4  | H1.20   | 0   | UTX0. Serial data out at +3.3V logic levels. Output from the BBB's           |

| 10.4  | П1.20   | )   | UART5_TXD.                                                                   |

| 10.5  | H1.19   | ı   | URX0. Serial data in at +3.3V logic levels. Input to the BBB's UART5_RXD.    |

| 10.6  | H1.18   | 0   | UTX1. Serial data out at +3.3V logic levels. Output from the BBB's           |

| 10.6  | П1.10   | O   | UART1_TXD.                                                                   |

| 10.7  | H1.17   | ı   | URX1. Serial data in at +3.3V logic levels. Input to the BBB's UART1_RXD.    |

| 10.8  | H1.16   |     | Not connected.                                                               |

| 10.9  | H1.15   |     | Not connected.                                                               |

| 10.10 | H1.14   |     | Not connected.                                                               |

| 10.11 | H1.13   |     | Not connected.                                                               |

| 10.12 | H1.12   | 0   | -urtso. Request-to-send (RTS) serial handshake at +3.3V logic levels,        |

| 10.12 | 111.12  | U   | active low. Output from the BBB's UART5_RTSn.                                |

| 10.13 | H1.11   | 1   | -uctso. Clear-to-send (CTS) serial handshake at +3.3V logic levels, active   |

| 10.15 | 1111.11 | '   | low. Input to the BBB's UART5_CTSn.                                          |

| 10.14 | H1.10   | 0   | -urts1. Request-to-send (RTS) serial handshake at +3.3V logic levels,        |

| 10.11 | 111.10  | 0   | active low. Output from the BBB's UART1_RTSn.                                |

| 10.15 | H1.9    | 1   | -ucts1. Clear-to-send (CTS) serial handshake at +3.3V logic levels, active   |

| 10.15 | 111.3   | '   | low. Input to the BBB's UART1_CTSn.                                          |

| 10.16 | H1.8    | 0   | UTX2. Serial data out at +3.3V logic levels. Output from the BBB's           |

|       |         | )   | UART2_TXD.                                                                   |

| IO.17 | H1.7    | ı   | URX2. Serial data in at +3.3V logic levels. Input to the BBB's UART2_RXD.    |

| 10.18 | H1.6    | I   | General-purpose input. Input to the BBB's GPIO2_1.                           |

| 10.19 | H1.5    | 0   | UTX4. Serial data out at +3.3V logic levels. Output from the BBB's           |

|       |         | )   | UART3_TXD.                                                                   |

| 10.20 | H1.4    |     | Not connected.                                                               |

| IO.21 | H1.3    |     | Not connected.                                                               |

| IO.22 | H1.2  |       | Not connected.                                                              |  |  |  |  |

|-------|-------|-------|-----------------------------------------------------------------------------|--|--|--|--|

| 10.23 | H1.1  |       | Not connected.                                                              |  |  |  |  |

| 10.24 | H2.24 | 0     | General-purpose output. Output from BBB's GPIO2_22.                         |  |  |  |  |

| 10.25 | H2.23 | 0     | General-purpose output. Output from BBB's GPIO2 23.                         |  |  |  |  |

| 10.26 | H2.22 | 0     | General-purpose output. Output from BBB's GPIO2_24.                         |  |  |  |  |

| IO.27 | H2.21 | 0     | General-purpose output. Output from BBB's GPiO2 25.                         |  |  |  |  |

| 10.28 | H2.20 |       | Not connected.                                                              |  |  |  |  |

| 10.29 | H2.19 |       | Not connected.                                                              |  |  |  |  |

| 10.30 | H2.18 | 0     | General-purpose output. Output from BBB's GPIO1_29.                         |  |  |  |  |

| 10.31 | H2.17 |       | Not connected.                                                              |  |  |  |  |

| 10.32 | H2.16 | 0     | UTX3. Serial data out at +3.3V logic levels. Output from the BBB's          |  |  |  |  |

| 10.32 | П2.10 | O     | UART4_TXD.                                                                  |  |  |  |  |

| 10.33 | H2.15 | ı     | URX3. Serial data in at +3.3V logic levels. Input to the BBB's UART4_RXD.   |  |  |  |  |

| 10.34 | H2.14 |       | Not connected.                                                              |  |  |  |  |

| 10.35 | H2.13 |       | Not connected.                                                              |  |  |  |  |

| 10.36 | H2.12 |       | Not connected.                                                              |  |  |  |  |

| 10.37 | H2.11 |       | Not connected.                                                              |  |  |  |  |

| 10.38 | H2.10 |       | Not connected.                                                              |  |  |  |  |

| 10.39 | H2.9  |       | Not connected.                                                              |  |  |  |  |

| IO.40 | H2.8  | ı     | AN0 analog input at maximum +1.8Vdc. Direct input to BBB's AIN0.            |  |  |  |  |

| IO.41 | H2.7  | -     | AN1 analog input at maximum +1.8Vdc. Direct input to BBB's AIN1.            |  |  |  |  |

| IO.42 | H2.6  |       | AN2 analog input at maximum +1.8Vdc. Direct input to BBB's AIN2.            |  |  |  |  |

| 10.43 | H2.5  | I     | AN3 analog input at maximum +1.8Vdc. Direct input to BBB's AIN3.            |  |  |  |  |

| IO.44 | H2.4  | ı     | AN4 analog input at maximum +1.8Vdc. Direct input to BBB's AIN4.            |  |  |  |  |

| IO.45 | H2.3  | I     | AN5 analog input at maximum +1.8Vdc. Direct input to BBB's AIN5.            |  |  |  |  |

| 10.46 | H2.2  | I     | AN6 analog input at maximum +1.8Vdc. Direct input to BBB's AIN6.            |  |  |  |  |

|       |       |       | -BUFF_EN. When high (+3.3V), indicates that BBB's I/O is in a high-         |  |  |  |  |

| IO.47 | H2.1  | 2.1 O | impedance state relative to the CSK bus connector. When low (0V), indicates |  |  |  |  |

|       |       |       | that BBB's I/O to the CSK bus connector is active.                          |  |  |  |  |

# **CubeSat Kit Bus PIN DESCRIPTIONS – Analog References**

| Name  | Pin    | I/O | Description                                                     |  |  |  |  |  |  |

|-------|--------|-----|-----------------------------------------------------------------|--|--|--|--|--|--|

| VREF0 | H1.26  | 0   | ADC reference voltage. Connected to BBB's VDD_ADC. The positive |  |  |  |  |  |  |

| VICEE | 111.20 |     | reference voltage (+1.8Vdc) for the BBB's ADC system.           |  |  |  |  |  |  |

| VREF1 | H1.28  |     | Not connected.                                                  |  |  |  |  |  |  |

| VREF2 | H1.30  |     | Not connected.                                                  |  |  |  |  |  |  |

# CubeSat Kit Bus PIN DESCRIPTIONS – Reserved

| Name  | Pin   | 1/0 | Description    |  |  |  |  |  |

|-------|-------|-----|----------------|--|--|--|--|--|

| RSVD0 | H1.44 | _   | Not connected. |  |  |  |  |  |

| RSVD1 | H1.45 | -   | Not connected. |  |  |  |  |  |

# CubeSat Kit Bus PIN DESCRIPTIONS - I2C Bus

| Name    | Pin   | 1/0 | Description                          |  |  |  |  |

|---------|-------|-----|--------------------------------------|--|--|--|--|

| SDA_SYS | H1.41 | I/O | 2C data. From/to the BBB's I2C1_SDA. |  |  |  |  |

| SCL_SYS | H1.43 | 0   | I2C clock. From the BBB's I2C1_SCL.  |  |  |  |  |

# CubeSat Kit Bus PIN DESCRIPTIONS - Control & Status

| Name    | Pin   | I/O | Description                                                                                                                                                                                                                                 |

|---------|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -FAULT  | H1.25 | 0   | Open-collector output from MBM2's latchup-prevention overcurrent switch. Active LOW. Wire-ORed signal.                                                                                                                                      |

| SENSE   | H1.27 | _   | Current sense signal. Can be used to measure MBM2's + BBB's current consumption. The current drawn from +5 $v_sys$ is (+5 $v_sys - sense$ ) / 75 $m\Omega$ .                                                                                |

| -RESET  | H1.29 | I/O | Input to reset supervisor. Output from MBM2 if sw1 is fitted (non-default). An active signal (0Vdc) on this input will reset the BBB if/when the BBB has enabled its bus reset input via GPIO1_14.                                          |

| OFF_VCC | H1.31 | ı   | Input to latchup-prevention overcurrent switch. Output from MBM2 if sw1 is fitted (non-default). An active signal (+5Vdc) on this input will disable +5V_SYS power to the BBB if/when the BBB has enabled its bus reset input via GPIO1_14. |

| PPS     | H1.46 |     | Not connected.                                                                                                                                                                                                                              |

# **CubeSat Kit Bus PIN DESCRIPTIONS – RBF and Separation Switches**

| Name       | Pin            | I/O | Description    |

|------------|----------------|-----|----------------|

| s0         | H2.33<br>H2.34 |     | Not connected. |

| s1         | H2.35<br>H2.36 |     | Not connected. |

| S2         | H2.37<br>H2.38 |     | Not connected. |

| <b>s</b> 3 | H2.39<br>H2.40 |     | Not connected. |

| S4         | H2.41<br>H2.42 |     | Not connected. |

| <b>S</b> 5 | H2.43<br>H2.44 |     | Not connected. |

# CubeSat Kit Bus PIN DESCRIPTIONS - Power

| Name    | Pin                     | 1/0 | Description                                                                                                   |  |  |  |  |  |

|---------|-------------------------|-----|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| VBATT   | H2.45<br>H2.46          |     | Not connected.                                                                                                |  |  |  |  |  |

| +5V_USB | H1.32                   | I/O | +5V USB power. From USB host. Powers local circuitry.                                                         |  |  |  |  |  |

| +5V_SYS | H2.25<br>H2.26          | I   | +5V system power. Powers the BBB and local circuitry.                                                         |  |  |  |  |  |

| PWR_MHX | H1.33                   |     | Not connected.                                                                                                |  |  |  |  |  |

| VBACKUP | H1.42                   | 0   | Battery backup voltage (e.g. for RTC). From MBM2's 3V Lithium battery BT1.                                    |  |  |  |  |  |

| vcc_sys | H2.27<br>H2.28          | I   | VCC System power. Assumed to be +3.3V. Used only as a configurable pull-up voltage for I2C.                   |  |  |  |  |  |

| AGND    | H2.31 I                 |     | Analog ground. Connected to BBB's GNDA_ADC. Provides the negative reference voltage for the BBB's ADC system. |  |  |  |  |  |

| DGND    | H2.29<br>H2.30<br>H2.32 | -   | Digital ground.                                                                                               |  |  |  |  |  |

# CubeSat Kit Bus PIN DESCRIPTIONS - Transceiver Interface

| Name     | Pin   | 1/0 | Description    |  |  |  |  |  |

|----------|-------|-----|----------------|--|--|--|--|--|

| -RST_MHX | H1.34 |     | Not connected. |  |  |  |  |  |

| -CTS_MHX | H1.35 |     | Not connected. |  |  |  |  |  |

| -RTS_MHX | H1.36 |     | Not connected. |  |  |  |  |  |

| -DSR_MHX | H1.37 |     | Not connected. |  |  |  |  |  |

| -DTR_MHX | H1.38 |     | Not connected. |  |  |  |  |  |

| TXD_MHX  | H1.39 |     | Not connected. |  |  |  |  |  |

| RXD_MHX  | H1.40 |     | Not connected. |  |  |  |  |  |

# **CubeSat Kit Bus PIN DESCRIPTIONS – User-defined**

| Name   | Pin   | I/O | Description    |

|--------|-------|-----|----------------|

| USER0  | H1.47 |     | Not connected. |

| USER1  | H1.48 |     | Not connected. |

| USER2  | H1.49 |     | Not connected. |

| USER3  | H1.50 |     | Not connected. |

| USER4  | H1.51 |     | Not connected. |

| USER5  | H1.52 |     | Not connected. |

| USER6  | H2.47 |     | Not connected. |

| USER7  | H2.48 |     | Not connected. |

| USER8  | H2.49 |     | Not connected. |

| USER9  | H2.50 |     | Not connected. |

| USER10 | H2.51 |     | Not connected. |

| USER11 | H2.52 |     | Not connected. |

### **PHY PIN DESCRIPTIONS**

### PHY PIN DESCRIPTIONS - Transceiver Interface

|            |         |     |       | 5V/3.3V |                                                   |  |  |

|------------|---------|-----|-------|---------|---------------------------------------------------|--|--|

| Name       | Pin     | I/O | RS422 | LVTTL   | Description                                       |  |  |

| PHY_XMT3   | J263.1  | 0   |       | •       | User-defined. Always from gpIO2 10.               |  |  |

| GND        | J263.2  |     |       |         |                                                   |  |  |

| PHY_XMT4   | J263.3  | 0   |       | •       | User-defined. Always from gpio2_11.               |  |  |

| GND        | J263.4  |     |       |         |                                                   |  |  |

| PHY_RCV2   | J263.5  |     |       | •       | User-defined. Always to gp102_12.                 |  |  |

| GND        | J263.6  |     |       |         |                                                   |  |  |

| PHY_RCV3   | J263.7  |     |       | •       | User-defined. Always to gp102_13.                 |  |  |

| GND        | J263.8  |     |       |         |                                                   |  |  |

|            | J263.9  |     |       |         | Configurable as +5V or +3.3V. Enabled when        |  |  |

| VDD_PHY    | J263.10 |     |       |         | BBB's sys_resetn is inactive/HIGH and             |  |  |

|            | J203.10 |     |       |         | GPIO1_16 is active/HIGH.                          |  |  |

| -PHY_RESET | J263.11 | 0   |       |         | When configured, tied to -RESET via an RC filter. |  |  |

| PHY_RXD    | J263.12 | ı   |       | •       | Serial input to BBB.                              |  |  |

| PHY_TXD    | J263.13 | 0   |       | •       | Serial output from BBB.                           |  |  |

| GND        | J263.14 |     |       |         |                                                   |  |  |

| PHY_XMT2   | J263.15 | 0   |       | •       | User-defined. Always from gpIO2 9.                |  |  |

| SCL_SYS    | J263.16 | 0   |       |         | From/to I2C signals on CSK connector.             |  |  |

| SDA_SYS    | J263.17 | I/O |       |         | From/to 12C signals on CSK connector.             |  |  |

| PHY_XMT1+  | J263.18 | 0   | •     |         | From uart1_rtsn, uart2_txd, Spi1_sclk or not      |  |  |

| PHY_XMT1-  | J263.19 |     |       |         | used.                                             |  |  |

| PHY_RCV1-  | J263.20 |     | _     |         | TO HARMI CHES HARMS BYD CRIOI 38 OF NOTHERD       |  |  |

| PHY_RCV1+  | J263.21 | '   | •     |         | To uart1_ctsn, uart2_rxd, gpio1_28 or not used.   |  |  |

| PHY_XMT0+  | J263.22 | 0 • |       |         | From uart1 txD, spi1 do or not used.              |  |  |

| PHY_XMT0-  | J263.23 |     |       |         | TIOHI OARTI_TXD, SPII_DO OF HOLUSEU.              |  |  |

| PHY_RCV0-  | J263.24 |     | •     |         | To uart1_rxd, spi1_di or not used.                |  |  |

| PHY_RCV0+  | J263.25 | '   |       |         | 10 OAKII_KAD, BIII_DI OI HOUGGU.                  |  |  |

### Compatibility

MBM2 has been tested with and is intended for use with the following instances of the open-source BeagleBone Black design: 12

| Manufacturer   | Product Name / ID            | Supported? | Notes                                                  |

|----------------|------------------------------|------------|--------------------------------------------------------|

| CircuitCo, LLC | BeagleBone Black®            | yes        | Rev C. Digi-Key® P/N BB-BBLK-000-REVC-ND <sup>13</sup> |

| Seeed Studio   | BeagleBone Black® Industrial | yes        | SKU 102110423. Digi-Key® P/N 1597-102110423-ND         |

| Element 14     | BeagleBone Black             | no         |                                                        |

#### **Power**

The MBM2 draws its power from the CSK's +5v\_sys and/or +5v\_usb, and uses the resultant +5Vdc power to generate a local 3.3V (vcc) as well as to power the BBB at +5Vdc. +5Vdc power drawn from +5v\_sys is current-limited and will automatically trip and reset if the setpoint is exceeded. vcc is used to drive peripherals on the MBM2 (e.g., RTC and SD Card) and to establish the I/O voltage level for the BBB.

+5Vdc power can also be applied (at any time) via the BBB's barrel jack connector P1 and/or its mini-USB device connector. <sup>14</sup> The various power possibilities are shown below. The BBB is on whenever a +5V power source (internal or external) is connected to the MBM2+BBB.

| Bus power enabled | USB Host connected | External +5V power input at P1 | +5V_SYS<br>power | +5V_USB<br>power | BBB<br>status |

|-------------------|--------------------|--------------------------------|------------------|------------------|---------------|

|                   |                    |                                | off              | off              | off           |

| •                 |                    |                                | on               | off              | on            |

|                   |                    | •                              | off              | off              | on            |

| •                 |                    | •                              | on               | off              | on            |

|                   | •                  | •                              | off              | off              | on            |

|                   | •                  |                                | off              | on               | on            |

| •                 | •                  |                                | on               | on               | on            |

| •                 | •                  | •                              | on               | on               | on            |

Table 5: System & BBB power status based on +5V power sources

### Logic-level Interfacing to the BBB

The BBB's I/O operates at +3.3V LVTTL levels, referenced to the BBB's VDD 3V3B power bus.

All of the push-pull GPIO signals from the BBB to the CSK bus connector pass through unidirectional isolators on the MBM2 and present themselves as CSK bus signals at LVTTL signals referenced to local VCC (normally +3.3V). These isolators are enabled only when the BBB's bidirectional SYS\_RESETn signal is inactive, i.e. the BBB is no longer in reset. An inverted, unidirectional version of SYS\_RESETn is provided as the -BUFF EN output on the CSK bus connector.

When interfacing to any of the BBB's signals mapped to the CSK bus connectors IO. [39..0] signals, note that all are inactive / high-impedance until -BUFF\_EN is active. Based on warnings included with each BBB, it's possible that the prohibition on connecting any signals to the BBB's inputs before its has come out of reset also applies to the analog inputs AIN[6..0]; the -BUFF\_EN signal can be used to gate analog signals that connect to AIN[6..0].

BBB open-collector / open-drain signals like I2C1's SDA and SCL signals are connected directly to the CSK bus connector; no isolators are involved.

-

<sup>&</sup>lt;sup>12</sup> See <u>beagleboard.org</u> for more information.

<sup>13</sup> It's unclear whether this Digi-Key part number is a generic one for all Rev C BeagleBone Blacks, or just the ones from CircuitCo.

<sup>&</sup>lt;sup>14</sup> This assumes that the EPS connected to the CSK bus connector can handle external +5V power sources on +5v\_sys. This is often true.

#### **PHY Transceiver Interface**

The PHY consists of four RS422 signals (2 outputs and 2 inputs), five 5V/3.3V LVTTL BPIO signals (3 outputs and 2 inputs), UART0 or UART2 at 5V/3.3V LVTTL levels, the system I2C bus, and power, ground and a reset signal. This PHY interface is power-on-reset protected, and is enabled only when GPIO1 16 is active/HIGH and the BBB's SYS RESETD signal is inactive/HIGH.

VDD\_PHY can be configured as 3.3V (default) or 5V. All of the PHY's single-ended signals will have a maximum possible voltage swing of VDD\_PHY. VDD\_PHY can also be used to provide power for any active circuitry or other powered electronics on the other end of the interface, but this is not recommended. +3.3V is sourced from the BBB's 3.3V output (VDD\_3V3B, on P9 pins 3&4), +5V is sourced from +5v\_sys.

Since RS232, RS422 and GPIO in general are point-to-point type connections, these signals on the PHY transceiver interface must be configured at the factory to avoid conflicts with the source/destination signals on the CSK bus. For example, the first PHY\_XMT/RCV RS422 signal pair can be configured as UART1\_TXD/RXD or as SPI1\_DO/DI, but in both cases, the chosen signals will be isolated at the factory from the CSK bus connector. Similarly, the LVTTL UART0\_TXD/RXD pair can be omitted, as can the I2C SCL\_SYS/SDA\_SYS pair. Contact the factory for more information.

An example configuration for the PHY transceiver interface is shown below. This is for a high-speed RF transceiver that has an SPI interface as its high-speed data interface, and several GPIO signals for lower-speed signaling.

| Signal Name |             |            |                                     |

|-------------|-------------|------------|-------------------------------------|

| MBM2        | PHY / BBB   | Direction  | Signal Function                     |

| PHY_XMT0    | SPI_MOSI    | BBB → PHY  | RS422 SPI data out to transceiver   |

| PHY_RCV0    | SPI_MISO    | BBB ← PHY  | RS422 SPI data in from transceiver  |

| PHY_XMT1    | SPI_SCLK    | BBB → PHY  | RS422 SPI clock                     |

| PHY_RCV1    | SPI_RDY     | BBB ← PHY  | RS422 SPI ready from transceiver    |

| PHY_XMT2    | SPI_FS      | BBB → PHY  | LVTTL SPI chip select               |

| PHY_XMT3    | SelProgSW_0 | BBB → PHY  | LVTTL Firmware select bit 0         |

| PHY_XMT4    | SelProgSW_1 | BBB → PHY  | LVTTL Firmware select bit 0         |

| PHY_RCV2    | RcvState_0  | BBB ← PHY  | LVTTL Receive state indicator bit 0 |

| PHY_RCV3    | RcvState_1  | BBB ← PHY  | LVTTL Receive state indicator bit 1 |

| SCL_SYS     | I2C_SCL     | BBB → PHY  | I2C clock                           |

| SDA_SYS     | I2C_SDA     | BBB ←→ PHY | I2C data                            |

| PHY_TXD     |             | BBB → PHY  |                                     |

| PHY_RXD     |             | BBB ← PHY  | Not used                            |

| -PHY_RESET  |             | BBB → PHY  |                                     |

| VDD_PHY     |             |            |                                     |

Table 6: Sample signal functions for 25-pin PHY interface that requires SPI-over-RS422

Another example configuration for the PHY transceiver interface is shown below in Table 7. This maps the BBB's UART1 with RTS/CTS flow control to the RS422 PHY. Additional dedicated GPIO signals appear on the PHY as 3.3V LVTTL signals. UART0 (the BBB's boot/control terminal) is also presented on J263. Because they are mapped to J263, BBB UART0 and UART1 are not available on J132 and on the CSK bus connector, respectively.

| Signal Name |            |            |                                        |

|-------------|------------|------------|----------------------------------------|

| MBM2        | PHY / BBB  | Direction  | Signal Function                        |

| PHY_XMT0    | UART1_TXD  | BBB → PHY  | RS422 serial data out to transceiver   |

| PHY_RCV0    | UART1_RXD  | BBB ← PHY  | RS422 serial data in from transceiver  |

| PHY_XMT1    | UART1_RTSn | BBB → PHY  | RS422 flow control out to transceiver  |

| PHY_RCV1    | UART1_CTSn | BBB ← PHY  | RS422 flow control in from transceiver |

| PHY_XMT2    | GPIO2_9    | BBB → PHY  | LVTTL user-defined outputs             |

| PHY_XMT3    | GPIO2_10   | BBB → PHY  |                                        |

| PHY_XMT4    | GPI02_11   | BBB → PHY  |                                        |

| PHY_RCV2    | GPIO2_12   | BBB ← PHY  | LVTTL user-defined inputs              |

| PHY_RCV3    | GPI02_13   | BBB ← PHY  |                                        |

| SCL_SYS     |            | BBB → PHY  | Not used                               |

| SDA_SYS     |            | BBB ←→ PHY |                                        |

| PHY_TXD     | UARTO_TXD  | BBB → PHY  | LVTTL BBB debug/boot UART              |

| PHY_RXD     | UARTO_RXD  | BBB ← PHY  |                                        |

| -PHY_RESET  |            | BBB → PHY  | Not used                               |

| VDD_PHY     |            |            |                                        |

Table 7: Sample signal functions for 25-pin PHY interface that requires a serial RS422 connection with flow control

The PHY transceiver connector on the MBM2 is an Omnetics A29100-025. A mating, straight-through 18"/457mm harness is Omnetics A42631-025.

### Reset Supervisor

A local reset supervisor is provided. Its output is gated through the WDT interface (below) and is used to establish the power-on state of the power-up WDT block. A user-supplied pushbutton switch can be fitted to the MBM2 to enable manual resets of the BBB.<sup>15</sup>

## **Watchdog Timer Interface**

The MBM2 supports an external watchdog timer (WDT) that controls the system <code>-RESET</code> and/or <code>OFF\_VCC</code> signals. At power-on and whenever <code>-RESET</code> is active, the BBB is isolated from the effects of the <code>-RESET</code> and <code>OFF\_VCC</code> signals via a dedicated WDT interface; this allows the BBB to use its own local power-on/reset circuitry get through boot-up and other actions whose time-to-complete may exceed the external WDT's period. To allow external bus signals to reset and/or power-cycle the BBB, the BBB must explicitly clock the local <code>GPIO1\_14</code> signal <sup>16</sup> low-to-high at least once. This low-to-high transition unblocks the <code>-RESET</code> and <code>OFF\_VCC</code> signals so that when active, they can reset and power-down the BBB, respectively. Once the WDT interface is unblocked, the active-low <code>-RESET</code> signal will hold the BBB in reset as long as it is active, and the active-high <code>OFF\_VCC</code> signal will power-down the BBB and the MBM2 as long as it is active. The MBM2's WDT interface will remain in this state until a reset or system power-cycling event on <code>+5v\_sys</code>.

The off-board external WDT should be configured to drive **-reset** and/or **off\_vcc** active when the BBB has failed to kick the watchdog correctly. Typically, a GPIO output from the BBB to the external WDT is used to kick the WDT.

When the MBM2 is powered via USB, the OFF\_VCC signal is effectively disabled on the MBM2, and cannot power-cycle the BBB. The ability to reset the BBB via external WDT control of the ¬RESET signals remains.

#### **SD Card Interface**

An SD Card socket provides a 4-wire, SPI-mode SD Card interface to the BBB's spi1\_cs0, spi1\_do, spi1 di and spi1 sclk signals. The SD Card socket is connected directly to the CSK bus connector's

<sup>&</sup>lt;sup>15</sup> The BBB has its own reset button, though it is hard to reach when the BBB is mounted to the MBM2.

<sup>&</sup>lt;sup>16</sup> **GPIO1 14** is pulled down on the MBM2.

IO.[3..0] signals; therefore, it can be accessed by other devices as long as the chip select signal IO.0 driven by the BBB's SPI1 CS0 is under organized / arbitrated control.

The SD Card is powered from the local vcc (+3.3V).

The signal lines between the SD card and the BBB have no series resistors; therefore SPI clock speeds in the 20-50MHz range are possible, as long as they are supported by the SD Card.

#### **Real-Time Clock**

The 8-pin M41T81S RTC on the MBM2 functions as a slave I2C device and is connected directly to the CSK I2C bus (SDA\_SYS & SCL\_SYS); no I2C isolator is employed. A 3V Lithium coin-cell battery holder is present on the MBM2; when fitted, the VBACKUP power bus provides current-limited backup power to the RTC for the purpose of maintaining a real-time clock even when other power sources (+5V\_SYS, vcc sys, etc.) are not present.

### **Backup Battery**

The MB has a replaceable BR1225 3V Lithium coin cell to serve as a backup battery **BT1** for real-time clocks and other components requiring battery backup of volatile information.

Battery BT1 is held in place by a coin cell battery holder in one corner of the underside of the MB. The all-metal battery holder is oriented in such a way that once installed onto a CubeSat Kit Base Plate, the battery cannot slide out of its battery holder and is thereby physically restrained along five of six axes. However, since the battery has a conductive outer shell, excessive movement of the battery along its insertion / removal axis could result in a short if it were to contact the Base Plate. Therefore insulating Kapton tape and/or an epoxy or silicone adhesive should be applied to the battery and battery holder.

Alternately, the customer can feed **VBACKUP** on the CubeSat Kit bus via their own backup battery located elsewhere in the system.

### I2C

The BBB on the MBM2 normally functions as an I2C master controller on the BBB's 12C1 interface.

By default, I2C pull-ups of  $1.5k\Omega$  are connected to the MBM2's local **vcc** supply (+3.3V). Optionally, they can be connected to **vcc\_sys** (+3.3Vdc). See the MBM2 schematics for more information.

The MBM2 does not utilize the BBB's I2C0 (the I2C bus used for control interface, etc.). It remains free for the BBB to use locally.

The MBM2 does not utilize the BBB's I2C2 (the I2C bus used for Cape identification and enumeration). While I2C2 is pinned out on the BBB's P9, it overlaps the BBB's UART1\_RTSn and UART1\_CTSn signals. These signals pass through unidirectional isolators on their way to the CSK bus connector. Therefore I2C2 is not available on the CSK bus connector, even if the flow control features of the BBB's UART1 are not used.

### **BBB Cape Support**

Because the BBB is mounted "upside-down" on the MBM2 (i.e., the mating connectors for the BBB's P8 and P9 are male headers on the MBM2), and because of the I2C2–UART1 flow control overlap (see above), it is not possible to use standard BBB-compatible Capes with the MBM2+BBB.

### **BBB Analog Inputs**

All seven of the BBB's dedicated analog inputs AIN[6..0] are mapped to the CSK bus connector signals AN[6..0]. The reference voltage for the BBB's ADC (VDD\_ADC) is mapped to the CSK bus connector signal VREFO; this output can be used as an external reference voltage for other analog circuitry. Care must be exercised when applying analog voltages to the BBB if/when the BBB is in reset – see Logic-level Interfacing to the BBB, above.

### **Fitment**

The BBB is affixed to the MBM2 via a custom aluminum heatsink/spacer/heat spreader.

In some instances, the overall height of the module may be incompatible with certain stackups within a nanosatellite that expects to stack modules utilizing the standard 0.600" board-to-board spacing. In these situations, it may be necessary to trim the P8 and P9 header pins on the underside of the MBM2. It may also be necessary to remove some (unused) connectors of the BBB, e.g. the HDMI connector.

### **RBF and Separation Switches**

The MBM2 does not support RBF or Separation Switches – they must be accommodated elsewhere if/when required.

### **TRADEMARKS**

The following are Pumpkin trademarks. All other names are the property of their respective owners.

- Pumpkin™and the Pumpkin logo

- Salvo™ and the Salvo logo

- SUPERNOVA™

- MISC™

- CubeSat Kit™ and the CubeSat Kit logo

### **DISCLAIMER**

PUMPKIN RESERVES THE RIGHT TO MAKE ANY CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO CORRECT ERRORS AND IMPROVE RELIABILITY, FUNCTION, APPEARANCE OR DESIGN. PUMPKIN DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS. NOR THE RIGHTS OF OTHERS.

744 Naples Street San Francisco, CA 94112 USA tel: (415) 584-6360

fax: (415) 585-7948

web: <a href="http://www.pumpkininc.com/">http://www.pumpkininc.com/</a>

email: <a href="mailto:info@pumpkininc.com">info@pumpkininc.com/</a>

web: http://www.cubesatkit.com/

email: info@cubesatkit.com